# VISUALIZING PROGRAM MEMORY BEHAVIOR USING MEMORY REFERENCE TRACES

by

A.N.M. Imroz Choudhury

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

School of Computing

The University of Utah

August 2012

Copyright © A.N.M. Imroz Choudhury 2012

All Rights Reserved

THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# STATEMENT OF THESIS APPROVAL

The dissertation of A.N.M. Imroz Choudhury has been approved by the following supervisory committee members:

Paul A. Rosen, Steven G. Parker , Chair enter date

Date Approved

David M. Beazley , Member

Erik L. Brunvand, Member

Erik L. Brunvand , Member

Erik L. Brunvand , Member

Date Approved

Date Approved

Date Approved

Date Approved

# ABSTRACT

Computer programs have complex interactions with their underlying hardware, exhibiting complex behaviors as a result. It is critical to understand these programs, as they serve an important role: researchers use them to express new ideas in computer science, while many others derive production value from them. In both cases, program *understanding* leads to mastery over these functions, adding value to human endeavors. Memory behavior is one of the hallmarks of general program behavior: it represents the critical function of retrieving data for the program to work on; it often reflects the overall actions taken by the program, providing a signature of program behavior; and it is often an important performance bottleneck, as the the memory subsystem is typically much slower than the processor. These reasons justify an investigation into the memory behavior of programs.

A *memory reference trace* is a list of memory transactions performed by a program at runtime, a rich data source capturing the whole of a program's interaction with the memory subsystem, and a clear starting point for investigating program memory behavior. However, such a trace is extremely difficult to interpret by mere inspection, as it consists solely of many, many addresses and operation codes, without any more structure or context. This dissertation proposes to use *visualization* to construct images and animations of the data within a reference trace, thereby visually transmitting structures and events as encoded in the trace. These visualization approaches are designed with different focuses, meant to expose various aspects of the trace. For instance, the time dimension of the reference traces can be handled either with animation, showing events as they occur, or by laying time out in a spatial dimension, giving a view of the entire history of the trace at once. The approaches also vary in their level of abstraction from the hardware: some are concretely connected to representations of the memory itself, while others are more free-form, using more abstract metaphors to highlight general behaviors and patterns, which in turn characterize the program behavior. Each approach delivers its own set of insights, as demonstrated in this dissertation.

*For Ammu and Abbu*: a tiny token of my appreciation for their unrelenting love all the days of my life

# CONTENTS

| ABS | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | iii                                                |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ix                                                 |

| LIS | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xi                                                 |

| ACI | KNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xii                                                |

| СН  | APTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                  |

|     | <ul> <li>1.1 Abstraction, Behavior, and Performance</li> <li>1.2 The Memory Subsystem</li> <li>1.3 Visualization</li> <li>1.4 Thesis</li> <li>1.5 Dissertation Roadmap</li> <li>1.5.1 Concrete Visualization of Reference Traces with MTV</li> <li>1.5.2 Abstract Visualization of Reference Traces with Waxlamp</li> <li>1.5.3 Computing and Visualizing the Topological<br/>Structure of Reference Traces</li> <li>1.5.4 Visualizing Differential Behavior in Reference Traces</li> <li>1.6 Summary.</li> </ul> | 1<br>3<br>5<br>5<br>6<br>7<br>9<br>10<br>12<br>13  |

| 2.  | TECHNICAL BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                 |

|     | <ul> <li>2.1 Caching in Computer Systems</li> <li>2.1.1 CPU Memory Caches</li> <li>2.1.1.1 Cache Design and Operation</li> <li>2.1.1.1.1 Set associativity.</li> <li>2.1.1.1.2 Block replacement policy.</li> <li>2.1.1.1.3 Cache composition and operation.</li> <li>2.1.1.2 Cache Simulation</li> <li>2.2 Memory Reference Traces</li> <li>2.3 Program Instrumentation</li> </ul>                                                                                                                               | 15<br>16<br>17<br>17<br>19<br>20<br>21<br>22<br>22 |

| 3.  | RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                 |

|     | <ul> <li>3.1 Performance Modeling, Analysis, and Visualization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26                                                 |

|    | 3.2.1 Static Software Visualization                            | 26 |

|----|----------------------------------------------------------------|----|

|    | 3.2.1.1 Control Structure Visualization                        | 27 |

|    | 3.2.1.2 Visualizing Software Architecture                      | 27 |

|    | 3.2.1.2.1 Diagramming                                          | 27 |

|    | 3.2.1.2.2 Visualization                                        | 28 |

|    | 3.2.2 Dynamic Software Visualization                           |    |

|    | 3.2.2.1 Visual Programming and Debugging                       | 28 |

|    | 3.2.2.2 Algorithm Animation                                    |    |

|    | 3.2.2.3 Animation for Static Diagrams                          |    |

|    | 3.3 Reference Trace Processing                                 | 30 |

|    | 3.4 Hardware-Centric Visualization                             | 31 |

|    | 3.4.1 Execution Trace Visualization                            | 32 |

|    | 3.4.2 Memory Behavior and Cache Visualization                  | 32 |

| 4. | CONCRETE VISUALIZATION OF MEMORY REFERENCE TRACES WITH         |    |

|    | MTV                                                            | 34 |

|    | 4.1 Introduction                                               | 34 |

|    | 4.2 Memory Reference Trace Visualization                       |    |

|    | 4.2.1 System Overview                                          |    |

|    | 4.2.2 Visual Elements                                          |    |

|    | 4.2.2.1 Data Structures                                        |    |

|    | 4.2.2.2 Address Space                                          |    |

|    | 4.2.2.3 Cache View                                             |    |

|    | 4.2.3 Orientation and Navigation                               |    |

|    | 4.2.3.1 Memory System Orientation                              |    |

|    | 4.2.3.2 Source Code Orientation                                |    |

|    | 4.2.3.3 Time Navigation and the Cache Event Map                |    |

|    | 4.3 Examples                                                   |    |

|    | 4.3.1 Loop Interchange                                         |    |

|    | 4.3.2 Matrix Multiplication                                    |    |

|    | 4.3.3 Material Point Method                                    | -  |

|    | 4.4 Conclusions                                                |    |

| _  |                                                                | 77 |

| 5. | ABSTRACT VISUALIZATION OF MEMORY REFERENCE TRACES WITH WAXLAMP | 48 |

|    |                                                                | -  |

|    | 5.1 Introduction                                               | 48 |

|    | 5.2 Visualizing Reference Traces                               |    |

|    | 5.2.1 Structured Cache Layout                                  | 50 |

|    | 5.2.2 Data Glyph Behavior                                      |    |

|    | 5.2.2.1 Motion                                                 | 53 |

|    | 5.2.2.2 Color                                                  | 54 |

|    | 5.2.2.3 Size                                                   | 55 |

|    | 5.2.3 Time-Lapse Mode                                          | 55 |

|    | 5.2.4 Summary Views                                            | 56 |

|    | 5.3 Examples                                                   | 57 |

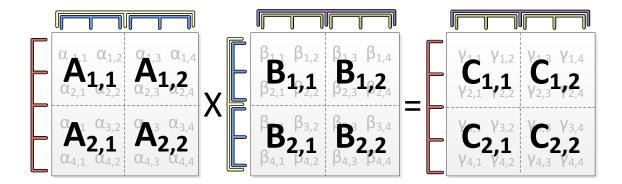

|    | 5.3.1 Matrix Multiply                                          |    |

|    | 5.3.1.1 Standard Algorithm                                     | 57 |

|    | 5.3.1.2 Transposed Matrix Multiply                             | 57 |

|    | 5.3.1.3 Blocked Matrix Multiply                                |    |

|    | 5.3.2 Sorting Algorithms                                       | 62 |

|    | 5.3.2.1 Bubble Sort                                                               | . 62  |

|----|-----------------------------------------------------------------------------------|-------|

|    | 5.3.2.2 Merge Sort                                                                | . 63  |

|    | 5.3.3 Material Point Method                                                       | . 64  |

|    | 5.4 Conclusions and Future Work                                                   | . 64  |

| (  |                                                                                   |       |

| 6. | COMPUTING AND VISUALIZING THE TOPOLOGICAL STRUCTURE OF<br>MEMORY REFERENCE TRACES | . 68  |

|    | 6.1 Introduction                                                                  |       |

|    | 6.2 Topological Analysis of Reference Traces                                      |       |

|    | 6.2.1 Encoding Memory Operations as a Point Cloud                                 |       |

|    | 6.2.2 Detecting Circular Features in a Point Cloud                                |       |

|    | 6.2.2.1 Step 1: Data Points to Simplicial Complex                                 |       |

|    | 6.2.2.2 Step 2: Simplicial Complex to Circular Coordinate Function                |       |

|    | 6.2.2.3 Step 2: Simplear Complex to Chediar Coordinate Function                   |       |

|    | 6.2.2.4 Intuitive Example                                                         |       |

|    | 6.2.2.5 Parameter Selection and Limitations                                       |       |

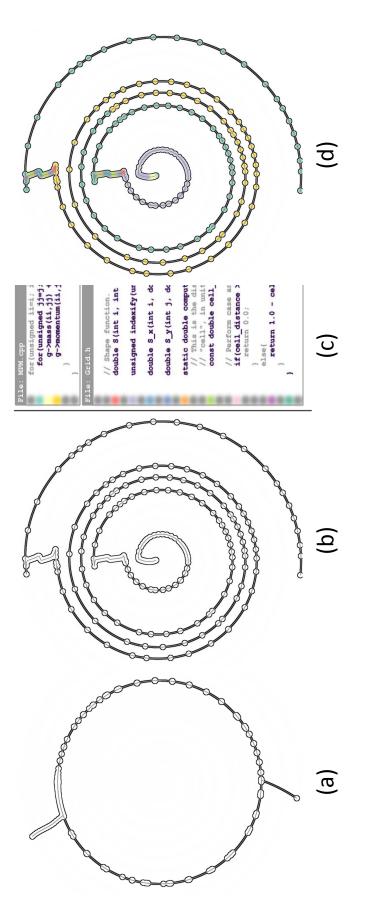

|    | 6.3 Visualizing Cycles in Reference Traces                                        |       |

|    | 6.3.1 Circular Visualization                                                      |       |

|    | 6.3.2 Spiral Visualization                                                        |       |

|    | 6.3.2.1 Correlation with Source Code                                              |       |

|    | 6.3.2.2 Morphing Between Parameterizations                                        |       |

|    | 6.4 Examples                                                                      |       |

|    | 6.4.1 Analyzing Loop Contents                                                     |       |

|    | 6.4.2 A Closer Look at Nested Loops                                               |       |

|    | 6.4.3 Nonloop-Based Recurrent Behavior                                            |       |

|    | 6.4.4 Analyzing Large Traces                                                      |       |

|    | 6.4.5 Performance-Related Behavior                                                |       |

|    | 6.4.6 Topological Persistence                                                     | . 89  |

|    | 6.5 Conclusions                                                                   | . 90  |

| 7. | VISUALIZING DIFFERENTIAL BEHAVIOR IN MEMORY REFERENCE TRAC                        | ES    |

|    | USING CACHE SIMULATION ENSEMBLES                                                  | . 91  |

|    | 7.1 Introduction                                                                  | . 91  |

|    | 7.2 Cache Performance Uncertainty                                                 | . 97  |

|    | 7.2.1 Data Features                                                               | . 98  |

|    | 7.2.2 Software Features                                                           | . 98  |

|    | 7.2.2.1 Choice of Algorithm                                                       | . 98  |

|    | 7.2.2.2 Data Layouts                                                              |       |

|    | 7.2.3 Architectural Features of Caches                                            | . 99  |

|    | 7.3 Visualizing Cache Simulation Ensembles                                        | . 100 |

|    | 7.3.1 Ensembles                                                                   | . 100 |

|    | 7.3.2 Time Matching                                                               |       |

|    | 7.3.3 Visual Diffs                                                                |       |

|    | 7.4 Examples                                                                      |       |

|    | 7.4.1 Comparing Data Layouts                                                      |       |

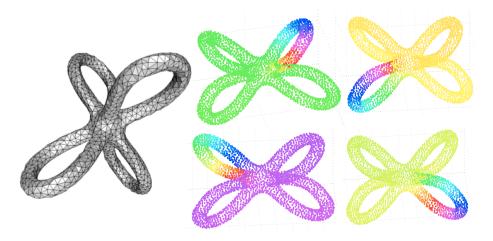

|    | 7.4.1.1 Rendering Triangle Meshes                                                 |       |

|    | 7.4.1.2 Material Point Method                                                     |       |

|    | 7.4.2 Comparing Algorithms                                                        |       |

|    | 7.4.2.1 Bubble vs. Insertion Sort                                                 |       |

|    | 7.4.2.2 Matrix Multiplication                                                     | . 107 |

|    | 7.4.3 Cache Size and Working Sets 108                                                                                                                                                                                                                       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

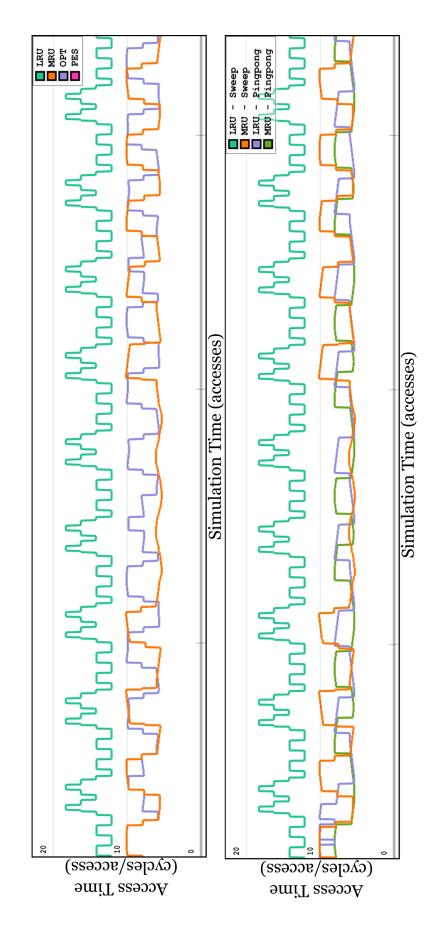

|    | 7.4.4 Block Replacement Policy                                                                                                                                                                                                                              |

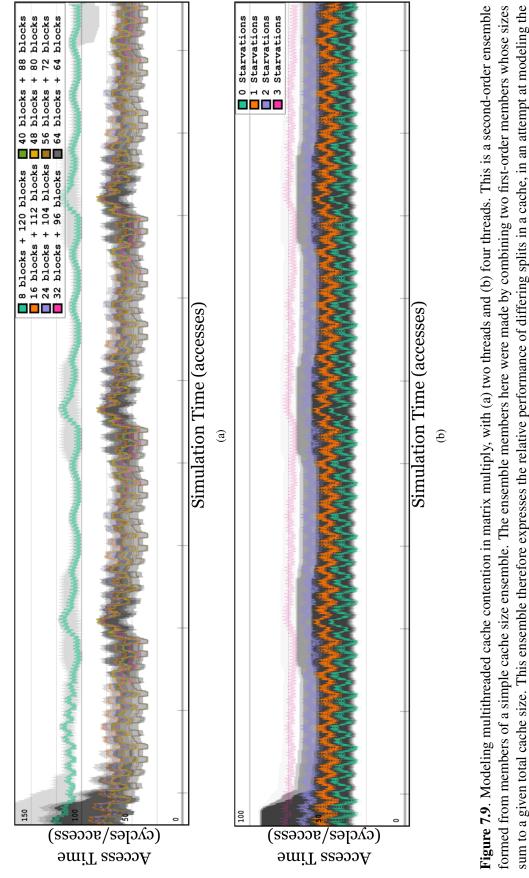

|    | 7.4.5 Second-Order Ensembles                                                                                                                                                                                                                                |

|    | 7.5 Conclusions                                                                                                                                                                                                                                             |

| _  |                                                                                                                                                                                                                                                             |

| 8. | DISCUSSION 123                                                                                                                                                                                                                                              |

|    | 8.1 MTV vs. Waxlamp                                                                                                                                                                                                                                         |

|    | 8.2 Handling the Time Dimension                                                                                                                                                                                                                             |

|    | 8.3 Summary of Visual Behaviors                                                                                                                                                                                                                             |

|    | 8.3.1 MTV                                                                                                                                                                                                                                                   |

|    | 8.3.2 Waxlamp                                                                                                                                                                                                                                               |

|    | 8.3.3 Topology                                                                                                                                                                                                                                              |

|    | 8.3.4 Ensemble                                                                                                                                                                                                                                              |

|    | 8.4 User Interfaces and Integration                                                                                                                                                                                                                         |

|    |                                                                                                                                                                                                                                                             |

| 0  |                                                                                                                                                                                                                                                             |

| 9. | CONCLUSIONS AND A LOOK TO THE FUTURE                                                                                                                                                                                                                        |

| 9. | CONCLUSIONS AND A LOOK TO THE FUTURE         131           9.1         Summary         131                                                                                                                                                                  |

| 9. |                                                                                                                                                                                                                                                             |

| 9. | 9.1 Summary                                                                                                                                                                                                                                                 |

| 9. | 9.1       Summary       131         9.2       Ideas for Future Work       132                                                                                                                                                                               |

| 9. | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings133                                                                                                                                                                             |

| 9. | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings1339.2.2Generalized Data Structure Layouts133                                                                                                                                   |

| 9. | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings1339.2.2Generalized Data Structure Layouts1339.2.3Enabling Performance Analysis133                                                                                              |

| 9. | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings1339.2.2Generalized Data Structure Layouts1339.2.3Enabling Performance Analysis1339.3Major Issues134                                                                            |

| 9. | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings1339.2.2Generalized Data Structure Layouts1339.2.3Enabling Performance Analysis1339.3Major Issues1349.3.1Data Scalability134                                                    |

| 9. | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings1339.2.2Generalized Data Structure Layouts1339.2.3Enabling Performance Analysis1339.3Major Issues1349.3.1Data Scalability1349.3.2Visualization Scalability135                   |

|    | 9.1Summary1319.2Ideas for Future Work1329.2.1Space-for-Time Visual Encodings1339.2.2Generalized Data Structure Layouts1339.2.3Enabling Performance Analysis1339.3Major Issues1349.3.1Data Scalability1349.3.2Visualization Scalability1359.3.3Evaluation135 |

# LIST OF FIGURES

| 1.1 | Memory Trace Visualizer (MTV) example                        | 8  |

|-----|--------------------------------------------------------------|----|

| 1.2 | Waxlamp example                                              | 11 |

| 1.3 | Topological approach example                                 | 12 |

| 1.4 | Ensemble approach example                                    | 14 |

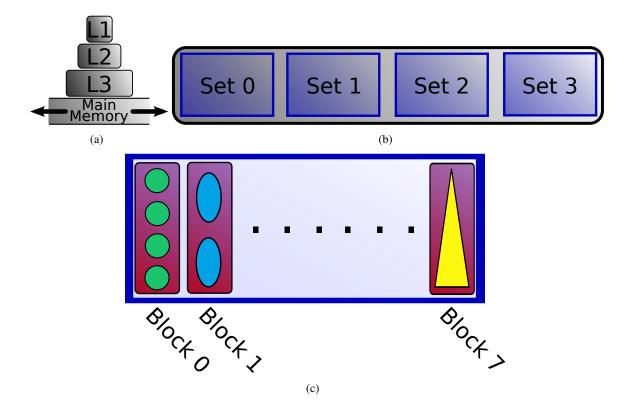

| 2.1 | The memory subsystem                                         | 18 |

| 4.1 | Screenshot of the Memory Trace Visualizer                    | 35 |

| 4.2 | Linear and matrix views of a memory region                   | 37 |

| 4.3 | Visualizing the address space                                | 38 |

| 4.4 | Visualizing the cache                                        | 40 |

| 4.5 | Cache event map                                              | 42 |

| 4.6 | Code examples for loop interchange                           | 43 |

| 4.7 | Comparing access orders for a two-dimensional array          | 44 |

| 4.8 | Comparing naive and blocked matrix multiplication            | 45 |

| 4.9 | Comparing storage policies for material point method         | 46 |

| 5.1 | Matrix multiply in various incarnations                      | 50 |

| 5.2 | Schematic structure of visualization design in Waxlamp       | 51 |

| 5.3 | Visualizing array initialization in Waxlamp                  | 52 |

| 5.4 | Visualizing the material point method in Waxlamp             | 54 |

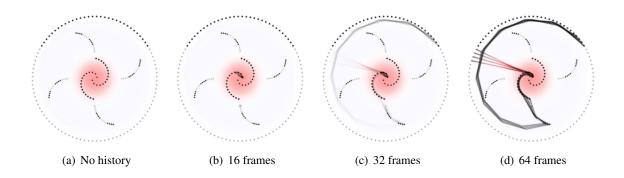

| 5.5 | History pathlines in Waxlamp                                 | 56 |

| 5.6 | Schematic view of access behavior in matrix multiplication   | 58 |

| 5.7 | Visualizing the cache behavior of bubble sort in Waxlamp     | 63 |

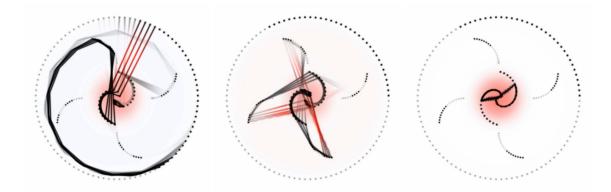

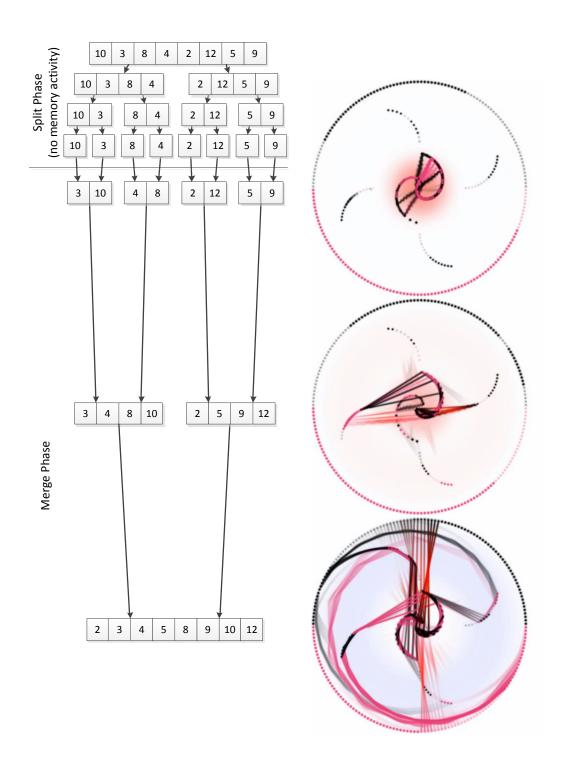

| 5.8 | Visualizing merge sort in Waxlamp                            | 65 |

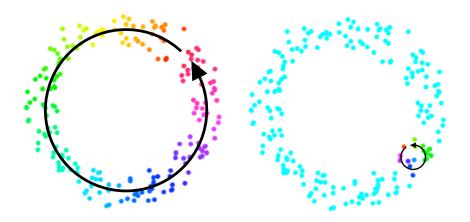

| 6.1 | Detecting cycles topologically                               | 72 |

| 6.2 | Comparison of high and low persistence cycles                | 73 |

| 6.3 | Detecting cycles in a genus-4 surface                        | 74 |

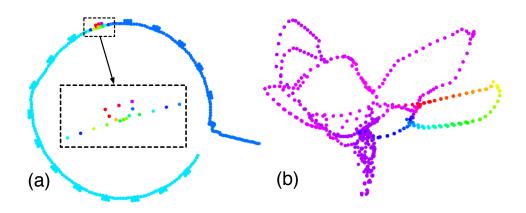

| 6.4 | Limited visualization of reference trace cycles using ISOMAP | 75 |

| 6.5 | Visualization options for reference trace cycle data         | 76 |

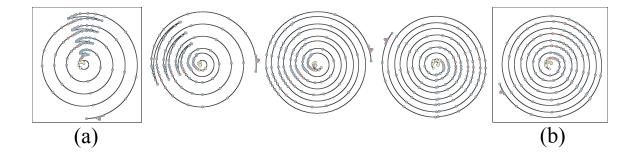

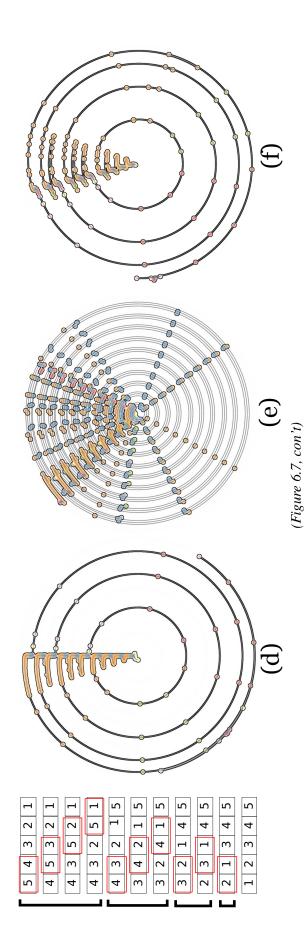

| 6.6 | Morphing between cycle parameterizations                     | 77 |

|     |                                                              |    |

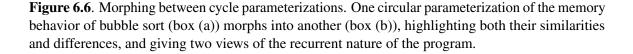

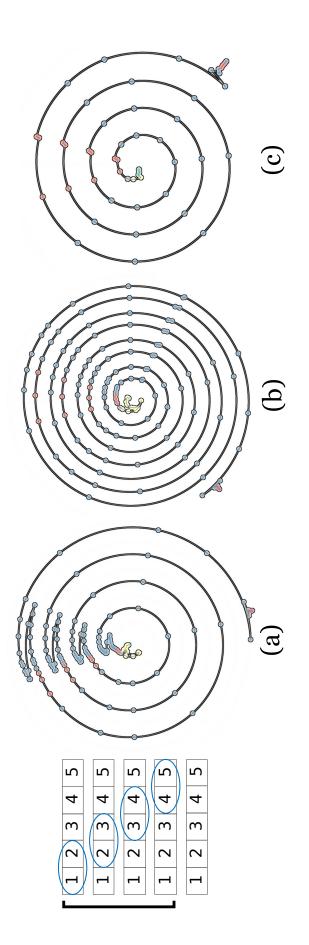

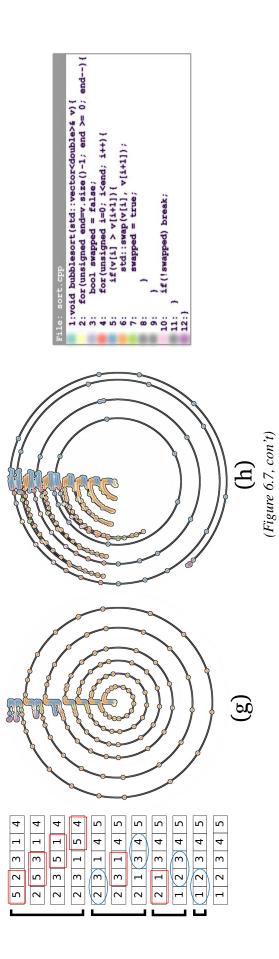

| 6.7  | Visualizing reference trace cycles in bubble sort                                   |

|------|-------------------------------------------------------------------------------------|

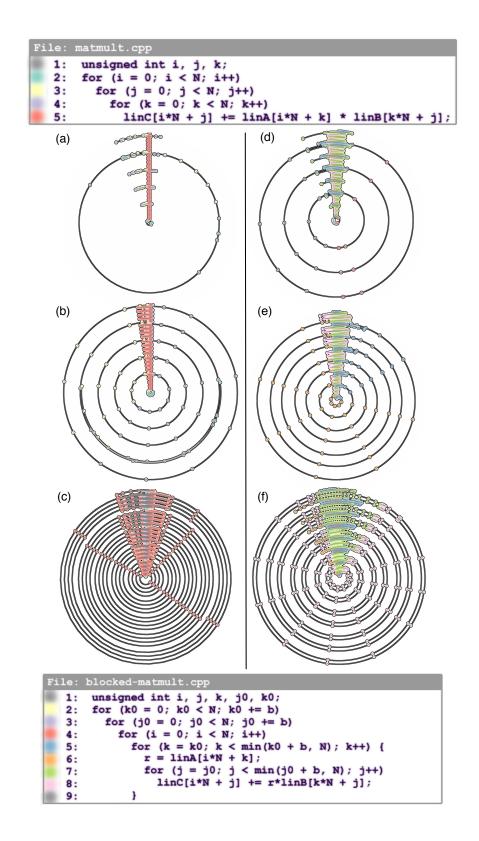

| 6.8  | Recurrent runtime structures in matrix multiplication algorithms                    |

| 6.9  | Block and loop structures in blocked matrix multiplication                          |

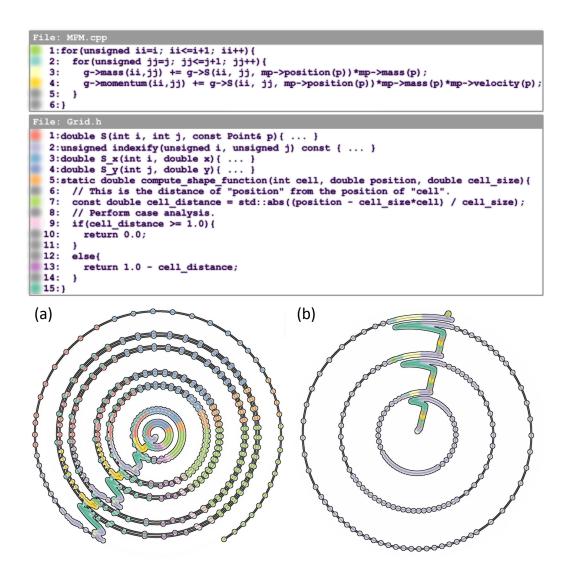

| 6.10 | Interpolating mass and momentum in MPM 87                                           |

| 6.11 | Visualizing MPM at longer time scales 88                                            |

| 7.1  | Overview of visualization for cache simulation ensembles                            |

| 7.2  | Sources of variation in cache performance                                           |

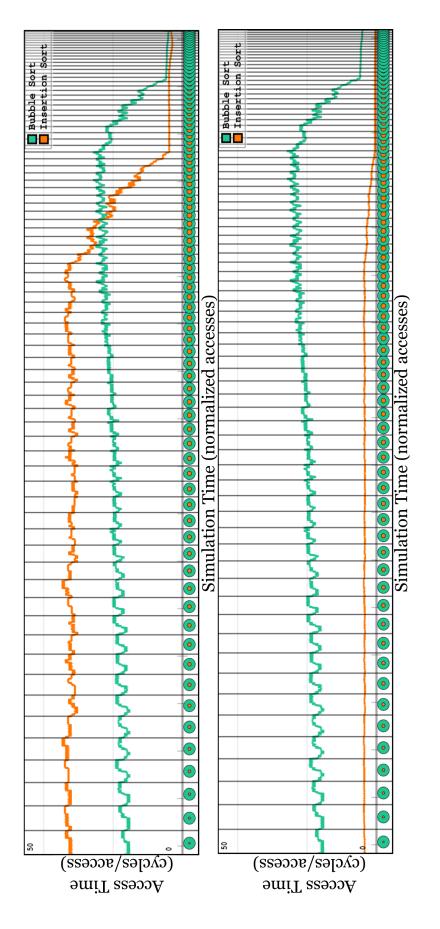

| 7.3  | Comparing bubble and insertion sort                                                 |

| 7.4  | Rendering triangles in different orders                                             |

| 7.5  | Data storage policies for MPM 106                                                   |

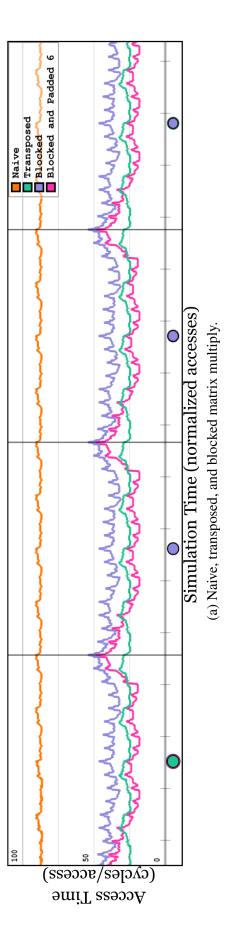

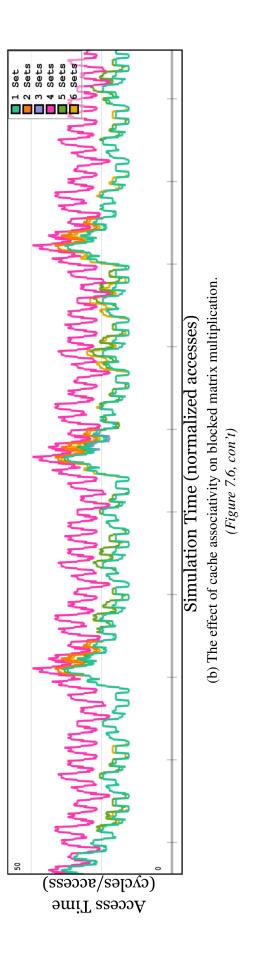

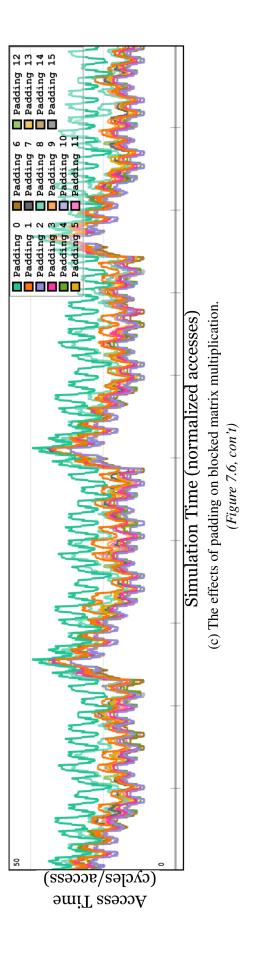

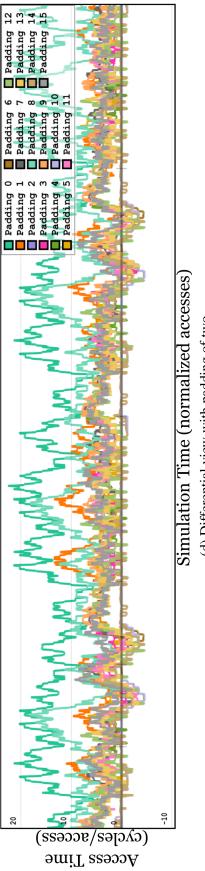

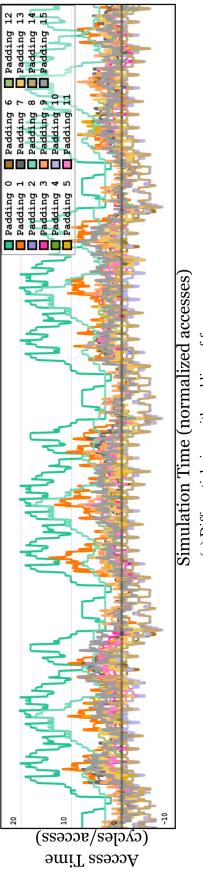

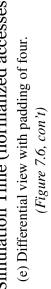

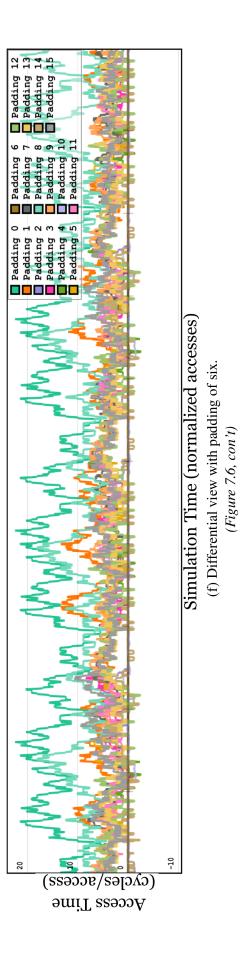

| 7.6  | Cache performance analysis of matrix multiplication                                 |

| 7.7  | Merge sort performance with different cache sizes                                   |

| 7.8  | Diffusion equation solver performance with different block replacement policies 119 |

| 7.9  | Modeling multithreaded cache contention in matrix multiply 121                      |

| 8.1  | A review of features of MTV and Waxlamp                                             |

# LIST OF TABLES

| 5.1 | Visual channels engaged in Waxlamp                            | 53 |

|-----|---------------------------------------------------------------|----|

| 6.1 | Details of the data used in topological analysis experiments. | 78 |

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my co-advisors, Steve Parker and Paul Rosen. I have worked with Steve for a long time, and he has always trusted and encouraged me to *think things* and *try them* on my own—to engage in true academic freedom during one of the few phases of my life when the opportunity is manifestly available to me. I have worked with Paul for a much shorter period of time, but I want to thank him for really helping to focus my efforts, while rolling up his own sleeves and marshalling both of our talents to really meet and destroy some research problems. Without their help, I am confident that I would not be here now, poised to defend this dissertation.

I would also like to express thanks to the other members of my dissertation committee, each of whom has brought me some subtle ideas about how to be a graduate student. Chris Johnson taught me the definite advantage and value of collaboration, which I have used to great effect during my time here. Mike Kirby has always reminded me of the importance of mathematics, even when it doesn't seem to figure strongly in my current work, and he has a certain practical approach to things, which I have tried to emulate to the extent that I can. Erik Brunvand seems to have a barely contained joy for his work, which is in itself inspirational, prompting me to look for it in my own work, and he had very encouraging words for me during the dark times of my journey to this dissertation. And last but not least, Dave Beazley's mantra of "a good thesis is a finished thesis" has helped me in these final months to keep my eyes on the prize and to take steady, stubborn steps towards it.

A special thanks for my paper co-authors throughout my graduate career: Jim Guilkey, Steve Parker, Valerio Pascucci, Kristi Potter, Paul Rosen, Mike Steffen, and Bei Wang. The most fun I had in graduate school was in working with others to speak out, shape, and improve ideas, and paper deadlines were some of my most satisfying moments.

During my time in graduate school, I have also had the enjoyable opportunity to work as a teaching assistant, and to see my field through the eyes of both teacher and student. For that opportunity I would like to thank Bob Kessler, who I worked with as a new graduate student, and Erin Parker, who I worked with as an old one. The chance to teach as well as conduct research gave me the full university experience, and for that I am grateful.

I would like to acknowledge my parents, to whom I complained more than once that my path to the end seemed literally impossible. They always dismissed the notion with such easy confidence that I had no choice but to stop complaining and take another step. Now that I have arrived, I am struck by the paradox of a seemingly impossible task being completed—but they knew it was possible all along.

And last, but not least, there are many others who deserve my gratitude—but I dare not name any of them here for fear of forgetting someone else. If you read this passage and feel defiance that I should mention your name here, then know that you have my implicit thanks for your part, however small, in helping make me who I am today. Graduate school is a roller coaster with exquisite peaks and dark valleys, and without the many, many good friends and colleagues I have acquired over the last eight years, it would not be properly bearable.

# **CHAPTER 1**

# **INTRODUCTION**

This dissertation is about spurring human understanding of program behavior—specifically, their *memory behavior*. Though the behavior a given program exhibits is a deterministic matter of the rules of operation of the computer system on which it runs, these rules give rise to extremely complex and—to a human observer—seemingly chaotic activity. Further complicating observed program behavior is the fact that a typical computer system runs several programs at the same time, as well as the operating system software that keeps everything else in line.

Memory behavior—the sum total of a program's interaction with the memory subsystem—is a critical component of overall program behavior, as it governs the retrieval and processing of program data, and can also represent a significant component of the time spent by a program in carrying out its tasks. Throughout this dissertation, the main data source is a *memory reference trace*, which is a list of memory accesses performed by a program as it runs. *Visualization*, the creation of images from data, is the major technique for prompting understanding and delivering insight about the data in a reference trace. This dissertation's main contribution is a series of visualization research ideas, each of which works to display some aspect of reference trace data, demonstrating what kinds of insights come from each.

The remainder of this chapter motivates the need for investigating program memory behavior, followed by a preview of the research approaches presented in this dissertation. Related work in the research literature, and matters of technical background are discussed before diving into the details of each approach. Then, some matters arising from comparison of the various research techniques will be discussed, before discussing future directions for the work, and concluding thoughts.

## 1.1 Abstraction, Behavior, and Performance

Abstraction is one of the computer scientist's greatest tools, enabling the use of complex systems purely through their interfaces, hiding the complexity within, and freeing the computer scientist to devote full mental effort to the problems at hand, rather than the tools being used. For example, the memory subsystem has a definite structure with rules of operation, servicing memory access requests through a translation lookaside buffer and several levels of cache. However, when writing software, the memory subsystem typically behaves like a single array of locations, pieces of which the programmer can invoke directly by name (through variables, array, or pointers, representing yet more layers of abstraction). Such a view of memory has much less structure than the actual memory system: it is an abstraction designed to free the programmer from worrying about how memory works, while still allowing correct access to memory—it hides the details of program behavior, instead allowing focus on the program *interfaces*.

This pattern recurs in every computer subsystem interface: secondary storage appears as a collection of filenames with pointers indicating where the next I/O operation occurs; a multiprocessor looks just like a single processor, with the programmer dispatching threads that are scheduled silently by the operating system; a cluster supercomputer looks like a collection of computers with unique identifiers, without the network topology that physiclal connects them together; a shared memory supercomputer presents a single memory address space to an application, even though different parts of that address space reside physically on different CPUs; and remote computers on a network look like files that can be written to and read from, to name just a few examples. In each case, the public interface hides a complex implementation layer that handles low-level tasks such as operating caches, spinning disks to the correct position, and breaking up and routing messages across a network, freeing programmers both from having to perform these tasks themselves, and from committing low-level errors while doing so.

In other words, presenting interfaces to computer subsystems is geared toward helping programmers produce *correct* programs. Generally speaking, however, this aid comes at a cost: for example, it is often the case that such abstractions make it more difficult for programmers to produce *efficient* programs. By design, the programmer's abstracted view of the computer lacks details of implementation that may suggest an efficient course of structuring computation. A common example is disregarding cache performance when considering how to build and access large, complex data structures. Because the memory access interface does not provide any feedback from the cache, the first choice is simply to forget about the cache, and in the pursuit of easy, correct code, efficient code loses out.

In certain cases, high performance is actually a software design goal. An application may need to be interactive in order to be usable at all (as for commercial graphics applications, such as real-time ray tracing), or the problem may be very large, only running on large government supercomputers on which runtime is scarce. In such cases, the definition of "correct program" includes not just a guarantee of *correct results*, but also of *quickly delivered results* as well.

Achieving a high-performance, correct program is nontrivial, however. Knuth warns that

"premature optimization is the root of all evil" [50]. Despite its age, the observation still holds true today: when programmers optimize prospective performance bottlenecks without verifying them as such first, the result can be little or no program speedup at the cost of newly obfuscated program code that will be difficult to maintain in the future, squandering the benefits of the programming abstractions. When high performance is required, the standard practice is to use a profiler to identify bottlenecks, then resolve them by reasoning about their causes. Generally speaking, that reasoning requires knowledge about the program's interactions with one subsystem or another; without such knowledge the programmer may make educated guesses, but the process is less informed and therefore less reliable. If such information about program behavior could be readily presented during software development, it could be used, for example, as a guide for optimization.

The central idea in this dissertation is to peel back the layer of abstraction offered by programming interfaces to capture and offer information about program behavior—and in particular, memory behavior—to the programmer. By collecting data about the underlying susystem during a program run, processing it to gain some insight into how the program behaves, programmers can immediately improve their own understanding of how a program works, and such understanding may equip them to improve their programs in some way beyond simple correctness, perhaps by applying the insight to program performance, or any other quality of the software that depends upon the implementations of the programmer's abstractions.

## **1.2** The Memory Subsystem

One of the most fundamental components of a computer system is the memory subsystem. Memory is critical to running programs, storing inputs, outputs, intermediate products of computation, and even the program code itself. Because the actual computation occurs in the CPU itself, with registers storing the immediate operands of each instruction, data and program code must be transferred from memory to the CPU to prepare for each operation, and results must be copied back into memory in order to correctly update program state.

However, the development trends of computer technology have produced a problem. Both memory and CPU speeds have been increasing exponentially, in accordance with Moore's Law [77], but at different exponential rates. Because the difference between two exponential functions is itself exponential, the trend has produced a widening gap between processor and memory performance, causing processors to be increasingly starved for data in more modern computer systems. This "memory wall" [97] represents the point at which the speed of a computer system would be wholly determined by the speed of its memory subsystem. In more recent years, rather than a continuing increase in processor speed, manufacturers have been placing more and more cores in each processor—

although now memory hardware has a chance to "catch up" to its faster colleague, now a new demand is placed upon the memory of feeding *several* cores with data, further complicating the relationship between processor and memory.

The standard solution to managing this widening speed difference has been the use of a *cache*. A cache is essentially a fast memory of limited size, representing an economic tradeoff between the slow, but extremely large main memory, and the very fast, yet extremely limited storage capacity of the register set present within the central processing unit. The cache greatly accelerates access to memory when requested data items are found in the cache more often than not. As noted earlier, the programming abstractions over main memory willfully omit information about the state of the cache, and generally speaking, the programmer has no control over the operation of the cache—it works silently behind the scenes, blindly storing a small subset of the program's working set.

Because it is left to the software engineer to reason about the contents and behavior of the cache without any good data, the cache can—and often does—represent a point of failure for program performance. The ubiquity of memory in all types of computers means the problem recurs in many settings. Poor use of cache in a single-threaded program can result in order-of-magnitude slowdowns, while on multiprocessors, poorly designed threads may cause the cache invalidation protocol to disrupt the performance of fellow threads. In shared memory supercomputers with non-uniform memory access (NUMA) architectures (in which the memory abstraction hides the fact that much of the memory accessible to a thread may lie on remote nodes) ignorant access patterns can block up the process while it waits for memory to be transferred from remote compute nodes. Cluster supercomputers require explicit transfer of memory between computers over some type of network, with even longer latencies than single-machine systems: poor use of memory can defeat the purpose of using a cluster in the first place. Even newer architectures, such as graphics processing units, suffer in performance if there are too many GPU-to-CPU memory transfers, or if the large number of threads do not use the uncached graphics memory properly.

When caching is not present, the programmer must carefully manage the memory behavior of the programs in order to achieve high performance; even when caching *is* present, the programmer must still understand how the system makes use of the cache to avoid getting in its way. In other words, in all cases, the programmer must understand the *behavior* of the memory system. Although caches generally have a small number of easily understood rules of operation (see Chapter 2)—they are simple enough that first-year students in computer science routinely learn about them—they often produce very complex behavior that may be difficult to reason about adequately, yet this behavior can be critical to achieving high performance. Here I give one example of a cache behavior that illustrates the extremes of the effect it can have on performance.

Simulation is a standard approach to analyzing a program's cache and memory behavior [92]. A simulated cache takes as input a *memory reference trace*, which is simply a list of memory addresses accessed by a program when it runs. A cache simulation yields gross numerical results about memory performance by reporting a small number of summarizing statistics, such as the overall cache miss rate, or the total amount of transfer bandwidth between memory and the simulated cache. Beyond simple summarizing statistics, however, the developer may wish to investigate the details of the simulation, i.e., the structure of the mixture of cache misses and hits produced by the simulation, as a function of time. In this view, the simulation produces a time-varying signal, constituting a data source reflecting the memory behavior of some program. To derive insight from this data, the developer needs some way to explore and understand its contents. This dissertation explores the use of *visualization* in different forms for performing such investigation.

### **1.3** Visualization

Visualization, the graphical representation of data, is a proven technique for making sense of large amounts of data and deriving insight from it [39]. Much of the work in visualization lies in designing *visual encodings*, i.e., deciding how to map features of the data to graphical parameters on the computer screen, such as position, color, size, etc. When the data itself has clear positional or spatial characteristics (such as in scientific simulations of particle systems [18]), some of these decisions are relatively easy to make. By contrast, *information visualization* deals in more abstract forms of data that may not have such obviously physical characteristics. Cache simulation data is one such example: different perspectives of how to represent the abstract events occuring in the simulation can result in different kinds of visualizations emphasizing one aspect of the data or another. Two such approaches are discussed in Chapters 4 and 5. A visualization approach focused more on the reference trace itself, and the insight that can be gained directly from it, is presented in Chapter 6, while Chapter 7 contains a more basic information visualization approach with the goal of *comparing* sets of simulations to gain insight from their differential performance.

## 1.4 Thesis

The ultimate goal of the work in this dissertation is to visualize the moment-to-moment, detailed memory behavior of some target program. Towards that end, memory reference traces are used as a basic data source, as well as the cache behavior information produced when such reference traces are used as input to a cache simulation. The former represents the basic interaction of a program with memory, while the latter provides a performance-oriented context. Such data contains information about individual, logical changes within the memory subsystem, and so provides memory behavior data at a very fine-grained level.

The memory behavior data is used as input to several visualization approaches focusing on various aspects of the behavior. Some examine the data at different levels of abstraction—providing either a more literal or more abstract view of the data, for example. Some take a closer perspective on the data than others, providing multiple viewpoints from which to derive insight about memory behavior at different scales. The visualization approaches lie at the heart of this dissertation, and its essential idea is summarized in the following thesis statement: **by using memory reference traces with carefully designed visual metaphors to display different aspects of program memory behavior, one can effectively visualize the fine-grained program memory behavior at different levels of abstraction from the hardware, leading to deeper understanding of the program.**

Visualization can be considered useful for three separate but related goals: education or explanation, confirming or disconfirming hypotheses, and exploratory analysis. The dissertation research presents novel approaches for visualizing memory behavior data, something that has not been done before at such a fine-grained level of detail; as such, it currently fits more into the first two categories than the third. Further work in this area will extend the techniques into independent, exploratory analysis.

Because the approaches are meant to induce human insight upon viewing images that are computed on-screen, some method of evaluating the visualization approaches is needed to measure their effectiveness. The current work has been validated via informal expert reviews by colleagues of the author who are moderately knowledgeable about the workings of computer systems—their reports indicate the initial effectiveness of these approaches.

## **1.5 Dissertation Roadmap**

In support of that thesis statement, this dissertation presents the story of my research. Chapter 2 presents some background about the pre-existing technologies and ideas critical to the work in this dissertation, focusing on memory reference traces, cache simulation, and software instrumentation. Chapter 3 discusses related work in the literature—both generally about software and information visualization, and in particular as related to the presented work—helping to contextualize the novel work presented here. Chapters 4 through 7 present the details of my dissertation research—a detailed description of the course of these chapters appears in the following subsection—before a discussion of the results and conclusions in Chapters 8 and 9, respectively.

The focus of this dissertation is the *memory behavior of programs*: how analyzing it can produce insight about applications, and how visualizing it can bring understanding of program behavior at large. The following outlines the story of the research presented in this dissertation, with detailed presentations appearing in individual chapters.

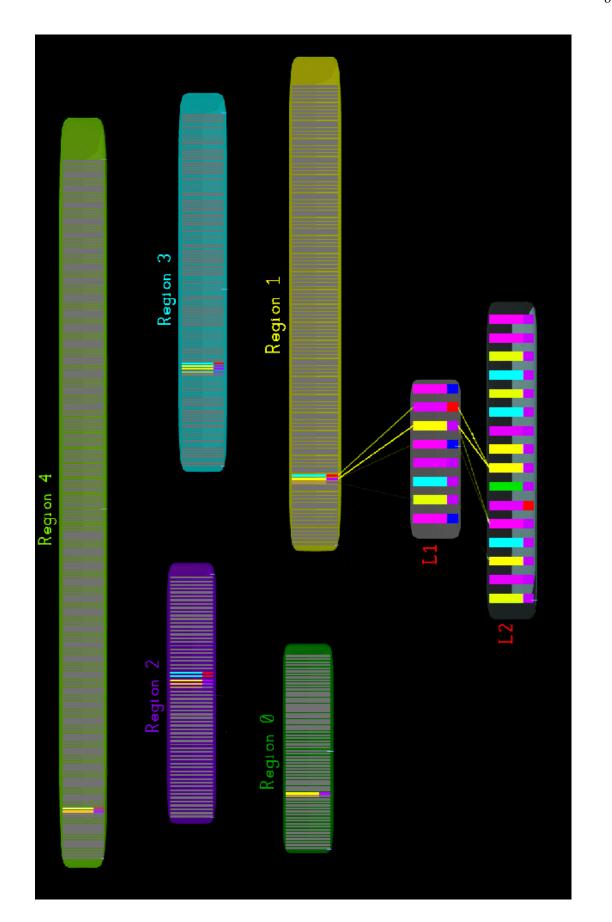

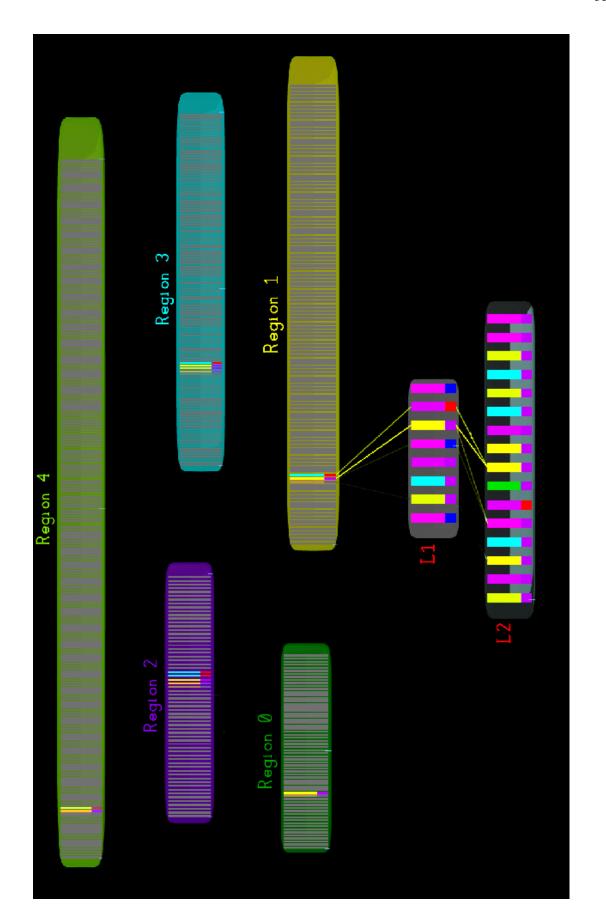

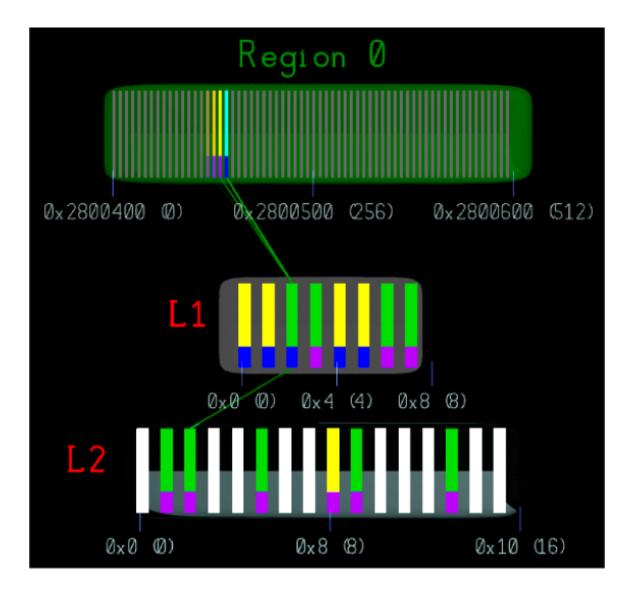

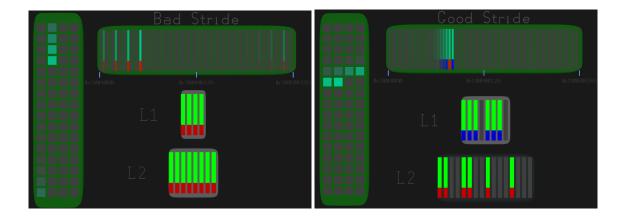

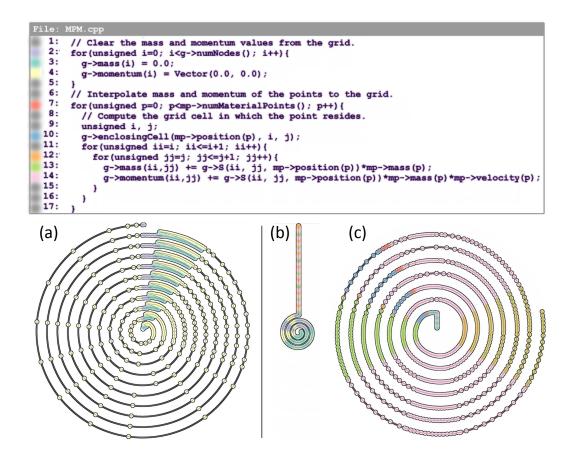

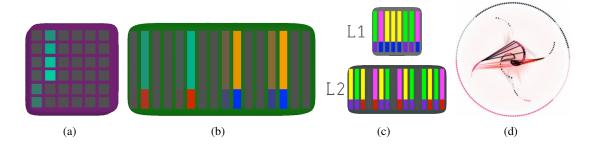

#### **1.5.1** Concrete Visualization of Reference Traces with MTV

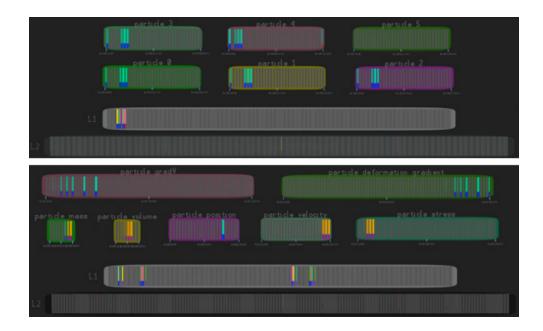

The Memory Trace Visualizer (MTV) [16] uses a dataflow model to receive memory reference trace data and transform it in various ways, feeding it to visualization objects and also through a cache simulation, resulting in a basic, concrete visualization of the reference data. MTV's main mode of operation has the developer inserting some instrumentation calls into the source code, so that when the program runs, it records the address and range of several memory regions of interest—these may either be arrays or individual variables. When the reference trace is collected, the regions of interest can be identified by their limiting addresses, and these can in turn be used to illuminate accesses in a graphical model of each region. The design of these models is straightforward: an array is visualized as a rectangular region of sequential data items, and as the trace is played back over the model, the cells representing data items light up in turn, visually display the access patterns encoded in the trace, rendering them visible to the developer. The abstraction of the memory subsystem is already that of a long array of locations; because MTV's visualization strategy does not substantially remap or transform the reference data to a different abstraction, MTV provides what might be termed a *literal* visualization. As such, MTV also serves as a baseline for the rest of the work in this dissertation, against which new approaches can be compared. An example image from MTV appears in Figure 1.1, showing a simulated cache at the bottom, with colored blocks indicating the data makeup of the cache contents, below several array-like regions of memory showing recent accesses encoded in a reference trace, visualizing the pattern of these accesses over time.

The major advantage conferred by MTV is that it allows the memory access patterns of a program—one of the major characterizaitons of its memory *behavior*—immediately and concretely visible to the user. Traditional software analysis teaches that certain types of access patterns are more favorable to the high-performance operation of a cache. In particular, contiguous access patterns allow for high data reuse, and predictable patterns, such as those with a constant stride, are able to be prefetched by specialized hardware within the memory subsystem: such patterns, or lack thereof, are easily seen in MTV, allowing for easier program behavior analysis.

MTV also introduces the idea of correlating events in the reference trace back to the lines of source code they are associated with. This mechanism comes directly from the operation of debuggers (such as the GNU Debugger, or GDB), where it is indispensable for contextualizing the events being investigated. In similar fashion, MTV plays back events visually, while also displaying a progression through the source code at run time. Though this simple idea is not novel, it is so useful a feature for maintaining the user's orientation within the trace that it is another feature that recurs throughout the dissertation research projects. It serves to anchor the user within the source code, which represents the software developer's most familiar way of interacting with the program.

Figure 1.1. Memory Trace Visualizer (MTV) example, showing memory accesses posting to a series of array-like memory regions.

Furthermore, MTV also uses a cache simulator to gather gross cache performance metrics, as well as informing a simple visualization of a cache glyph. This element of MTV absorbs the pre-existing technique of gathering summarizing statistics to provide large-scale indicators of performance. The cache visualization shows cache block residency by color coding the various regions of interest, with the cache level glyphs glowing to indicate the "warmth," or volume of data reuse, of each level. The idea of using cache simulation to drive the performance analysis of memory reference traces recurs throughout this dissertation, and first appears in MTV.

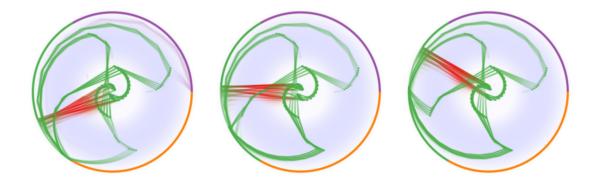

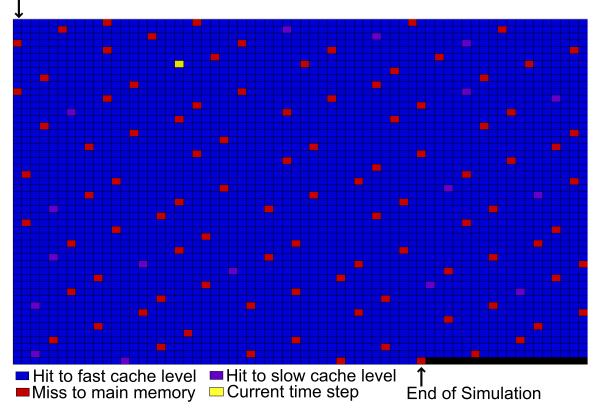

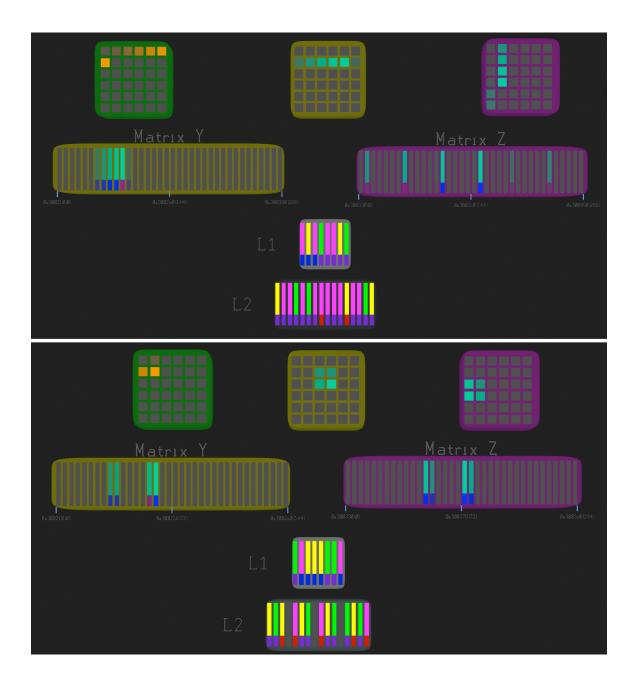

#### **1.5.2** Abstract Visualization of Reference Traces with Waxlamp

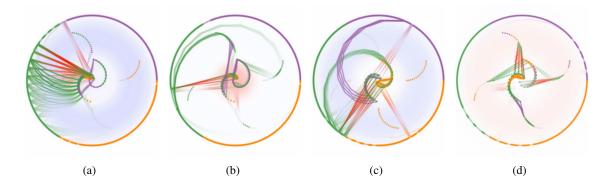

Waxlamp (Chapter 5, [17]) is a software system that sheds the "literal" view embodied in MTV for a more abstract visual approach. Whereas the focus of MTV was on the access patterns encoded the in trace, Waxlamp instead shifts the focus to the cache itself (which had been deemphasized in MTV). Waxlamp's major mode of visualization is a schematic, abstract view of the internal contents of the cache, with the CPU lying at the center of a radial dislay, and each cache level arranged in annular areas of increasing distance from the center, with the regions of interest lying in a bounding ring at a maximal radius from the center of the display. These regions are still color coded, as in MTV, but they are now more freeform, consisting of a set of point glyphs, one for each element of the array.

When reference trace records are played through the cache simulation, the visualization shows the result of each simulation step—that is, the motion of data between the levels of the cache, as data enters the lower levels, evicting data items to the higher levels, is computed and displayed. The motion of data is visualized by the point glyphs moving about the display, settling into their new homes in response to each step of the simulation. Each data glyph has a static origination point in the outer ring: the linear layouts of MTV have been transformed into a circular, but still linear, layout in Waxlamp. The access patterns so strongly showed by MTV are still visible in Waxlamp, but they have been deemphasized somewhat to make way for a focus on the actual data motion between levels of the cache. In particular, performance-related events such as cache hits and misses, are the new focus of this visualization, and they are marked visually by certain metaphorical characteristics. For example, a cache miss, by definition, retrieves data from the faraway main memory, moving it to the lowest level of cache. This is marked visually as a long journey of some data glyph from the outermost ring, to near the center of the display; it is furthermore flashed red on screen to redundantly encode the importance of the event in a different visual channel. Other dynamics of the cache simulation are also visualized in various visual channels: for example, the glyphs occupying some level of cache are arranged in spirals of increasing radius, with data items soon to be evicted by the replacement policy appearing at farther radii than new data that are not yet in line for eviction.

Because these visual designs are based less in the physical structure of the cache than in the data characteristics of interest to the developer, this visualization approach is more abstract than that offered by MTV. The abstractness leads to new patterns being visible. For instance, if a sequence of memory activity causes a high volume of cache misses-an important performance-related event—Waxlamp will show a flurry of data items flying in from the outer memory ring, with their motion trails lighting up red to highlight the volume of misses. By contrast, when the hit rate is high instead, this will be visualized as very localized activity nearer to the center of the display, leaving the faraway contents of main memory undisturbed. More complex patterns emerge as well: one unfortunate pattern of poor performance involves data being evicted from the cache that will soon be needed again. This would manifest as a peculiar pattern: data items at the outer edge of a cache level would be evicted to main memory, and then soon after re-enter the cache, resulting in a swooping exit-and-entry arc. Such patterns have an immediate meaning that signals the need for software analysis to the software engineer. Common program idioms, such as sweeping or striding access patterns, or heavy usage of a small stretch of memory locations, are also concretely visible in Waxlamp. Such an example appears in Figure 1.2, showing the initialization of a data array. The bundle of red lines shows data coming into the cache (towards the center) from main memory (the outer ring). As subsequent blocks are pulled in to be initialized, the bundle of red lines is seen to sweep clockwise around the arc of the green array in memory.

The flexible, abstract design of Waxlamp's high-level layout lends itself to other architectures and scales as well. If performance data about some system (GPU, cluster running MPI, I/O systems, etc.) can be collected, then it is possible to use Waxlamp's philosophy of encoding high-latency operations as farther distances to arrange the relevant components of the system, and play back the performance data over it. In other words, Waxlamp generalizes the MTV approach to any system in which data moves from place to place, and certain types or patterns of motion result in high or low performance.

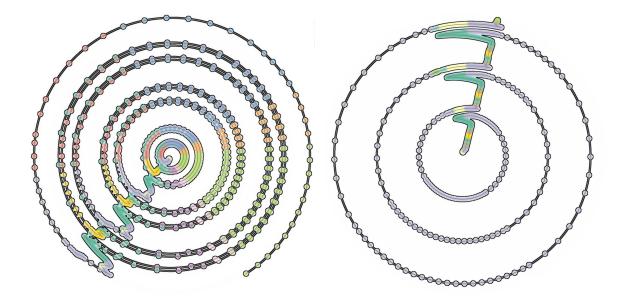

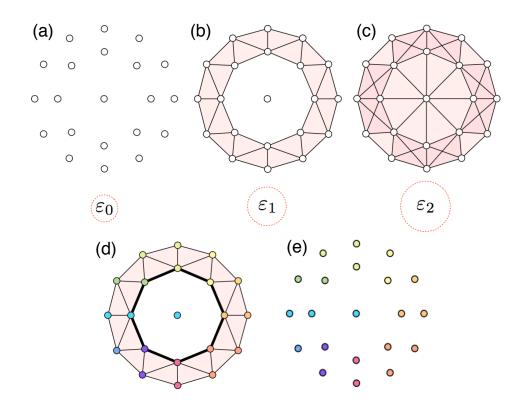

## 1.5.3 Computing and Visualizing the Topological Structure of Reference Traces

Setting aside cache simulation and the cache itself, a topological analysis approach allows focus on the structure of the reference trace itself (Chapter 6, [19]). A reference trace is nominally a one-dimensional, linear data source—a straightforward report of accessed addresses as a function of time. However, program flow, and programs themselves, are inherently *non*linear, typically executing loops, in which the flow repeats some number of times, and branches, which cause the flow to take one path or another through the program code.

Recurrence is an important feature of program execution that can manifest in the sequence of

**Figure 1.2**. Waxlamp example. A sequence of example images from the Waxlamp system, showing progress in initializing an array at the start of a program. The red incoming lines are showing blocks of data being brought into the cache to be written to; the lines can be seen to sweep around the circular arc representing the data array.

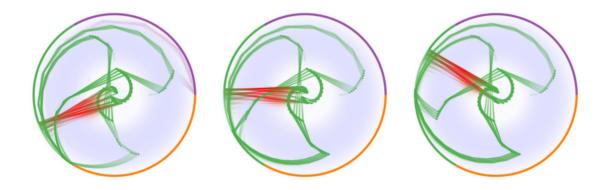

memory transactions, mapping to various types of program structures and behaviors, and also to operations that the memory hardware can try to optimize, such as prefetching. Such recurrences can occur at many program scales. For instance, a physical simulation may repeat a very long sequence of actions once per timestep, constituting a large-scale recurrence. By contrast, one of these actions may be an early data preparation step in which all the elements of some intermediate data array are initialized to zero, constituting a much smaller-scale recurrence. Detecting and visualizing such structures in the reference trace shows both the structure of the program itself, as well as exposing possibly unexpected recurrences that are not as apparent in the program code.

However, finding recurrences in the reference trace is not a simple matter of looking for regions of similarity within the trace—a recurrent behavior will repeat similar actions across some scale of unknown size, and may contain variations within each repetition due to branching or other effects, so that exact or even approximate matching techniques will not work. Instead, a topological approach that treats the reference trace as a higher-dimensional point cloud, then searches for circular paths of different sizes within it, can more effectively expose the recurrences.

The trace is converted to a point cloud by considering a sliding window of several memory references as single points. As the window slides, the group of memory transactions represents some sequence of actions at a particular time. In other words, the trace is converted from a singledimensional signal to a multidimensional one that encodes not just the actions taken at some moment, but the contextual actions taken *after* that time as well. The space in which these high-dimensional points live is then equipped with a metric function that expresses the similarity between two points, or groupings of memory activity. Within this metric space, the points are formed by proximity into a complex of simplices, which is then searched for circle-valued functions, which represent the possible recurrent behaviors. Sorting these cycles by their persistence reveals significant program structures.

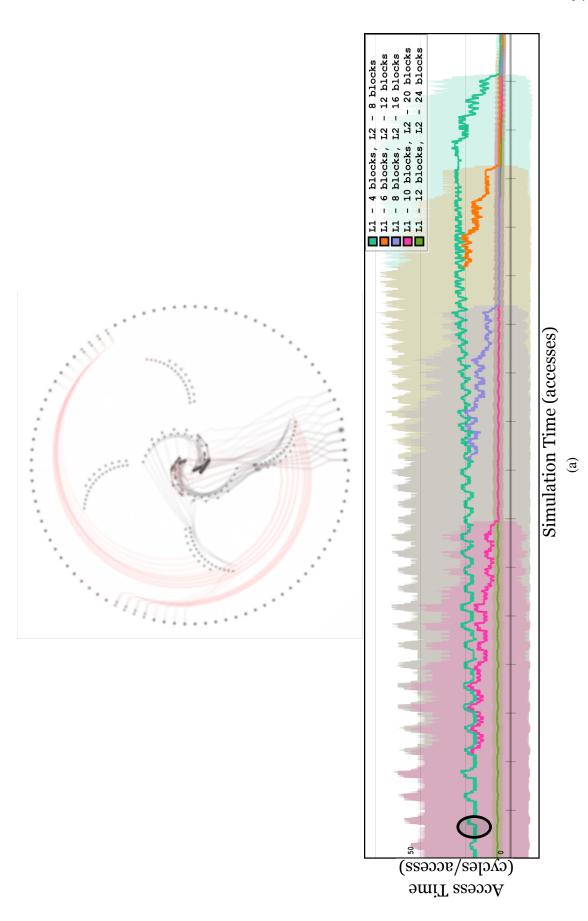

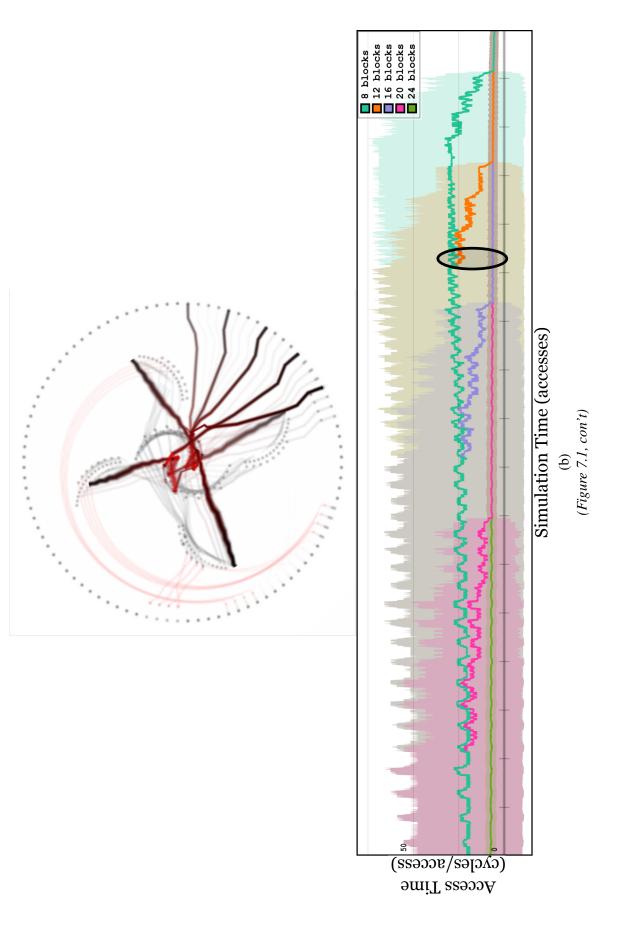

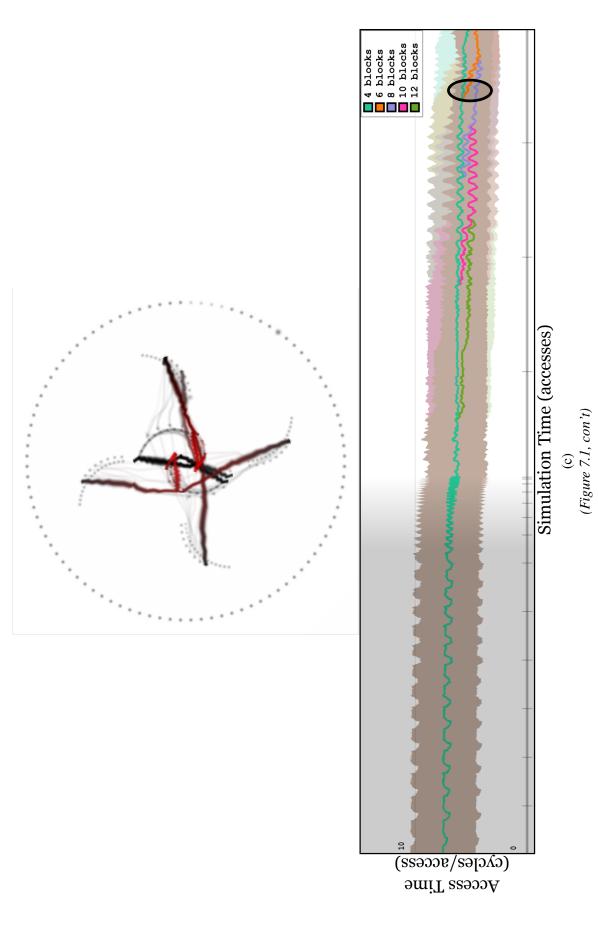

Each of the discovered cycles with sufficiently high persistence can be visualized in a spiral, where the angular position is given by the output from the topological method, and radius from the center determined by time. The result is a spiral shape representing the recurrent behavior, with other behaviors appearing within the spiral as nonspiral shapes. By shifting from one cycle to another, various recurrent behaviors can be visualized in the same space (Figure 1.3). These images serve as visual signatures of the recurrent behaviors in a given program, sometimes displaying unexpected or hidden program behavior, and in some cases even suggesting possible ways to restructure computation for higher efficiency.

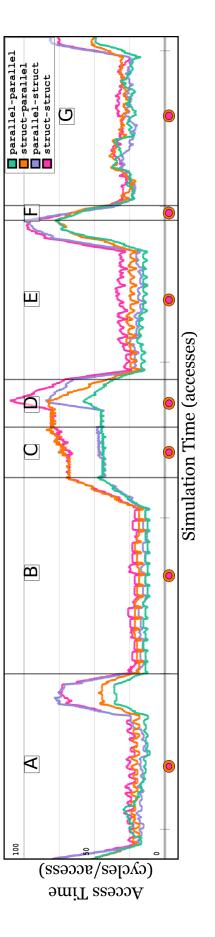

### 1.5.4 Visualizing Differential Behavior in Reference Traces Using Cache Simulation Ensembles

Finally, *cache simulation ensembles*—in which multiple reference traces are simulated in a cache, or a single reference trace is simulated in several cache configurations—are visualized to investigate the difference in behavior between the ensemble elements. Such ensembles are generally formed to scientifically test the variation of some variable. For example, simulating a reference

**Figure 1.3**. Topological approach example. Two examples of topological visualization of a portion of a reference trace, showing the interpolation of physical quantities from particles to a two-dimensional grid. The left image shows the repetitive nature of computing interpolation kernels in the x and y dimensions, while the right image emphasizes the noninterpolation activities in the expanding circles (showing the interpolation activity in the zigs and zags visible in the upper portions of each circle).

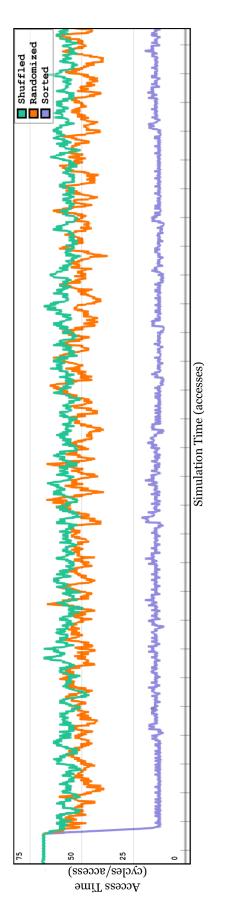

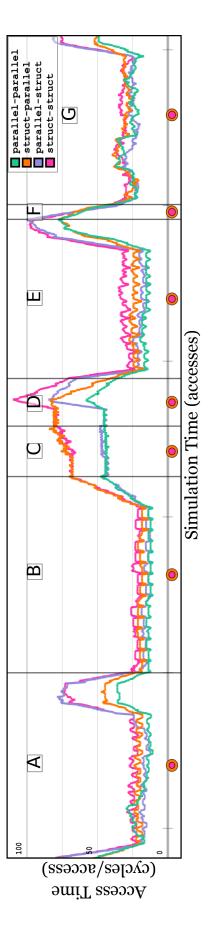

trace through several caches differing only in size enables a study of effect that cache size has on some algorithm. By contrast, reference traces from several implementations of the same algorithm can be simulated through a single cache to form an ensemble that enables the study of the relative memory performance of these implementation choices. In other words, this technique enables the study of differential performance due to some changing quality or quantity, using a straightforward comparative visualization of the ensemble to reveal performance differences.

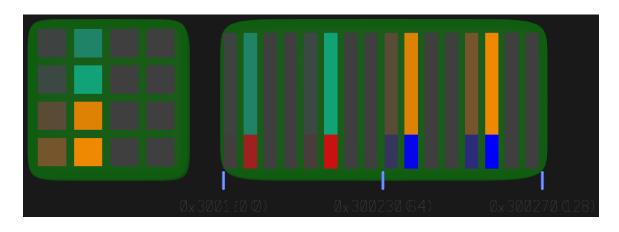

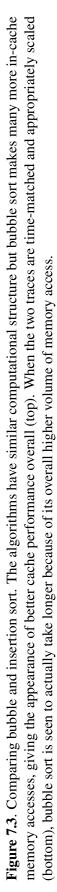

Generally speaking, a programmer has no control over the choice of cache that is used at run time. However, it is still useful to form and investigate the behavior of cache ensembles, as forming a differential may actually reveal unexpected features of the program execution, which *is* under the programmer's control. For example, changing the cache's block replacement algorithm in the cache ensemble may reveal that a particular replacement algorithm leads to optimal cache behavior for some algorithm. The cache ensemble analysis may suggest that some feature of the computation causes it to perform well under a different policy; the programmer may then realize that it is possible to restructure the computation in a nonobvious way so that it now aligns with the replacement that exists in the real cache. Such an example, along with many others, appears in Chapter 6. An example of the ensemble approach, focusing on different choices for data layout design, appears in Figure 1.4. As the curves deviate from each other, memory performance differentials resulting from the various choices are revealed.

The project also suggests a way to model the changing availability of resources at runtime due to the interference of operating systems and other processes, or processes such as cache invalidation occurring during multithreaded runs. In this approach, a cache ensemble is formed by changing the amount of some resource within the cache, such as size, emulating the eviction of entries due to contention for cache space among different threads in a process, or from competing processes. This approach may help to evaluate the performance stability of an algorithm to changes in available cache resources. Though promising, this approach requires further study for validation.

### **1.6 Summary**

This dissertation is driven by the idea that reference traces contain useful information about program behavior and performance, and that, although basic summarizing approaches such as cache simulation are useful in a basic way, visualization of the information in the reference traces leads to concrete insight and understanding of the programs under study.

This idea is revisited several times from different angles throughout this dissertation. The ultimate goal is that, in much the same way that interactive debuggers have eased the process of debugging, such techniques substantially ease the sometimes arcane practice of writing and running high-performance software.

Figure 1.4. Ensemble approach example. An example of visualizing a cache simulation ensemble, in which a particle system has its data storage laid out in four different ways. Where the curves deviate from each other, a memory performance differential is highlighted, providing evidence for or against a particular choice of layout. The lettered segments refer to various parts of the algorithm, in which different types of activity result in different memory behavior signatures.

## **CHAPTER 2**

# **TECHNICAL BACKGROUND**

This chapter discusses some existing technologies, techniques, and approaches that are made use of in this dissertation. In particular, the nature of *caching* is described, and how *software instrumentation* and *simulation* are used to produce *memory reference traces*, the fundamental source of data used for the research projects in this dissertation.

# 2.1 Caching in Computer Systems

Fundamentally, a *cache* is a fixed amount of storage for holding a limited number of copies of data items that are more permanently stored in some other place. The purpose of having a cache is to enable fast access to the cached data, as opposed to retrieving the same data items from their permanent storage locations.

Computer systems use many kinds of caches. Any time that data must be retrieved from its native source slowly, caches can be useful. For example, web browsers can keep cached copies of webpages whenever they are first loaded. Retrieving a local, cached copy of a webpage is much faster than retrieving the same page via network protocols from a remote machine—as the cached copy is loaded for the user to look at, the browser can begin to load a fresh copy from the network to make sure the user is looking at the newest version of the document. In this case, the local disk acts as a cache for the remote machine, where the "true" webpages reside.

The memory system can likewise serve as a cache for data residing on disk, since disk access latency is several orders of magnitude slower than memory access latency. For example, when launching a program, operating systems tend to load the program code and data into memory before beginning execution, rather than reading the program code directly from disk at runtime. However, there are also more application-specific uses of memory as a cache for the disk in cases when, for example, large amounts of data are being processed in random-access orders. For example, in large-scale visualization [13, 67] it may be necessary to predict which parts of the data will be needed in the near future, and therefore ensure that they are read from disk into memory, so that the algorithm can access them from memory rather than having to load them—much more slowly—from disk.

The memory system itself makes heavy use of caching to accelerate access to data residing there. These caches are usually implemented in hardware, as they have dedicated jobs with predefined rules of operation. For example, operating system level memory management uses a *translation lookaside buffer (TLB)* to accelerate the retrieval of memory pages for programs performing memory access. The operating maintains a page table—stored in a dedicated area of memory—to map from a program's virtual addresses to the physical memory addresses of the corresponding pages of memory. Without the TLB, for each memory access request, the operating system would have to consult the page table, and then look up the resulting physical page, roughly doubling the time spent in memory lookups. The TLB instead stores a small number of page table entries in a hardware cache, which can be looked up much faster than the page table itself. Because the TLB, like all caches, has a limited size, at some points during execution, the operating system will still need to consult the page table, but the presence of the TLB limits how often this must be done.

The example of the TLB hits upon one of the fundamental qualities of hardware caches: they are fast by necessity and design; however, their speed dictates that they also be either small, or expensive. For this reason, the major tradeoff in caching systems is between speed and size. This pattern recurs in other examples of hardware caches. For instance, NVIDIA graphics processing units (GPUs) contain two kinds of memory: "global memory" that is slow to access (taking on the order of hundreds of cycles) but very large, and a much smaller "shared memory" that can be accessed within just a few cycles. In older GPUs, the programmer has the option of using the shared memory as a cache, carefully managing what data is loaded into it from the slower global memory, striving to allow the processors to use this data as much as possible before loading in a new set of data from global memory. In fact, if the programmer does not use the shared memory as a cache, it is difficult or impossible to achieve the high-performance promise of the GPU. More recent models offer the alternative of automatic caching of global memory accesses, again in the shared memory, much like that found in CPU memory caches—the particular focus of this dissertation.

#### 2.1.1 CPU Memory Caches

In the manner of the caching examples discussed above, the CPU memory cache is used to store a small subset of data residing natively in memory to enable fast access to it, and as with the TLB, its major design tradeoff is in speed versus size. The idea behind this cache is that, as a program makes memory references, the CPU retrieves the requested data from the memory system (at great cost) and *caches* a copy in the cache. If the program happens to make another reference to the cached data, it can be retrieved—at relatively very little cost—from the cache instead of memory. The composition and arrangement of the cache is important to understanding how it works. For instance, when the cache is full, and an access to a nonresident piece of data is made, some decision needs to

be made about which resident piece of data to evict to make way for the new data. Because such design parameters have a definite and significant effect on performance, this section describes the components of a cache, how they work together, and the rules under which they operate to provide caching services for main memory.

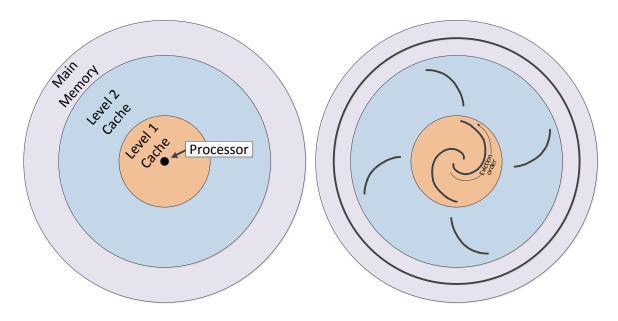

#### 2.1.1.1 Cache Design and Operation

The memory subsystem consists of main memory—a generally large array of locations in which data can be stored and manipulated when a program runs—and a *CPU memory cache* (Figure 2.1). The cache stores some subset of the contents of memory, enabling faster access to this subset. A cache consists of several *cache levels* arranged with a certain relationship, described below. When a program requests some data from the memory subsystem, it is first sought in the cache, level by level. If the data is found, it can be copied into the registers for use by the program immediately; if not, a sequence of protocols governs how the data is copied from main memory into the levels of the cache (possibly evicting some data that had been present in the cache already), and from there it can be copied into the registers as well.

Each cache level contains some amount of storage, divided into an array of fixed-size divisions known as *cache blocks* or *cache lines*. The size of a cache block is constant for all levels of a given cache. The cache block is the fundamental, atomic unit of data packaging for the memory system—that is, when a program makes an access to some address, it is the entire cache block containing that address that is copied from main memory into the cache. This is to take advantage of *spatial locality*, the notion that in typical programs, when an address is accessed, nearby addressed tend to be accessed soon after. In other words, by transferring a whole block, the cache tends to have related data ready for access.

Just as each location in memory has an address, so too do the cache blocks. The *block address* of the cache block containing a given location is simply some prefix of the address of the item at that location. As an example,  $0 \times 1000$  ccee is a 32-bit address for some location in memory. For 256-byte cache blocks, the containing block's address would be  $0 \times 1000$  ccef (with 256 addresses ranging from  $0 \times 1000$  cc00 to  $0 \times 1000$  ccff (with 256 addresses represented in the lower 8 bits).

**2.1.1.1.1 Set associativity.** To place a block of data into a level, the cache must decide which block it will occupy. The simplest placement policy is called *direct-mapping*, in which each block has a single place in the level it can go. Generally, the mapping is derived from the cache block address. Once more taking the example of cache block address 0x1000cc, and assuming a direct-mapped cache level of 128 cache blocks, the block would be placed in the  $0x1000cc \mod 128 = 76$ th block of the cache level.