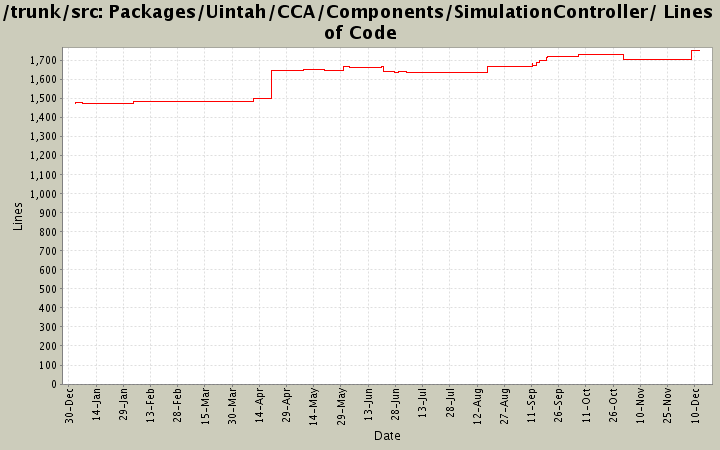

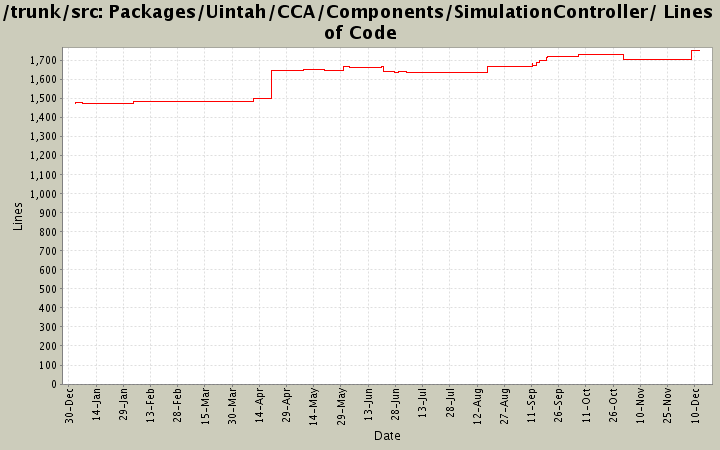

Lines of Code

[root]/Packages/Uintah/CCA/Components/SimulationController

| Author | Changes | Lines of Code | Lines per Change |

|---|---|---|---|

| Totals | 79 (100.0%) | 1436 (100.0%) | 18.1 |

| worthen | 57 (72.2%) | 1233 (85.9%) | 21.6 |

| luitjens | 11 (13.9%) | 78 (5.4%) | 7.0 |

| harman | 5 (6.3%) | 78 (5.4%) | 15.6 |

| dav | 1 (1.3%) | 33 (2.3%) | 33.0 |

| jas | 1 (1.3%) | 9 (0.6%) | 9.0 |

| guilkey | 1 (1.3%) | 3 (0.2%) | 3.0 |

| dgroulx | 3 (3.8%) | 2 (0.1%) | 0.6 |

Added the debug stream "IndividualComponentTimings" same as

"ComponentTimings" except per processor.

0 lines of code changed in 2 files:

Reformated output for easier parsing

1 lines of code changed in 1 file:

Add Per-Component LB stats for Regridder, LoadBalancer, TG Execution, TG mpi wait, TG compilation, available with SCI_DEBUG=ComponentTimings:+

68 lines of code changed in 3 files:

Fix small DLB bug resulting from last commit and remove debug print from AMRSC

0 lines of code changed in 1 file:

Remove concept of time-refinement from Grid, and store whether the sim is lockstep in SharedState. Have components compute delt based on the level it's on and have the SimulationController worry about the inter-level constraints. (Also consolidate SimCnt::doInitialTimestepRegridding into doInitialTimestep and doRegridding)

164 lines of code changed in 4 files:

d_movingAverage is now initialized... oops.

1 lines of code changed in 1 file:

Overhaul the DynamicLoadBalancer

State no longer maintained internally, called by SimController

Should now work with any combination of restart, regrid, nthproc,

timestep restarts, etc.

Schedulers:

Modify the way Particle Subsets determine whether they need to send

the number of particles to receiving processor

Don't reserve cell-refinement-ratio of cells for each var, just the

number of intra-level ghost cells required

MPMICE:

Move a cout to a cout_doing

Regridder:

Use Regridder vars on matl 0

4 lines of code changed in 1 file:

Replace Scheduler::noScrubVar and copyDataVar with overrideDefaultBehavior. Enable restarts to regrid where the old uda left off rather than waiting a timestep first

12 lines of code changed in 1 file:

Remove runtime warning (in DataArchive),

Display grid on restart if AMR debugstream is on,

Add some padding to refinementRatio so it doesn't round down (and throw an exception if a bad one is added)

5 lines of code changed in 2 files:

Force time-refinement to be based on cell refinement. This is probably temporary until we get the arbitrary-timestep per level working.

Also provides a "lockstep" knob for AMR that will in essence force TRR To be 1

Most of the changes are just moving adjustDelt from SimulationState back to Level.

20 lines of code changed in 2 files:

The mean is now calculated as the exponential moving average. Around 86% of

the weight occurs within the AVERAGE_WINDOW defined at the top of

SimulationContrller.cc.

The standard deviation has been removed because it no longer relates to

the mean.

27 lines of code changed in 3 files:

Improve the relationship between Load Balancing, Scrubbing, Multi-Taskgraphing, and refluxing

- Provide a Conditional message-send, which enables the TG to only compile once instead

of twice for a load-balance (and allows multi-tg to run following a lb)

- Have the LB threshold be based on the theoretical loadBalance%

- Deprecate nonCopyDataVars

23 lines of code changed in 2 files:

AMR Scrubbing

176 lines of code changed in 2 files:

Added the ability to specify a max_wall_time in the Time section. This

parameter is specified in seconds, omitting it or setting it to 0 will

cause it to be infinite.

2 lines of code changed in 1 file:

overwrite bad checkin

161 lines of code changed in 1 file:

override input.xml for reduce-uda instead of throw exception (and fix warning)

165 lines of code changed in 1 file:

Turn warning into an exception

2 lines of code changed in 1 file:

MPI fixes to Uda reducer

3 lines of code changed in 1 file:

Subcycle and coarsen only if doing AMR

13 lines of code changed in 1 file:

Changed the memory reporting from resident memory to total memory.

2 lines of code changed in 1 file:

(26 more)